🏠 Homework

2A

espresso script

.i 8

.o 4

.ilb a7 a6 a5 a4 a3 a2 a1 a0

.ob y2 y1 y0 z

.p 9

0 0 0 0 0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 1 0 0 0 1

0 0 0 0 0 0 1 0 0 0 1 1

0 0 0 0 0 1 0 0 0 1 0 1

0 0 0 0 1 0 0 0 0 1 1 1

0 0 0 1 0 0 0 0 1 0 0 1

0 0 1 0 0 0 0 0 1 0 1 1

0 1 0 0 0 0 0 0 1 1 0 1

1 0 0 0 0 0 0 0 1 1 1 1

.eResult

y2 = (a7&!a6&!a5&!a4&!a3&!a2&!a1&!a0) | (!a7&a6&!a5&!a4&!a3&!a2&!a1&!a0) | (!a7&!a6&a5&!a4&!a3&!a2&!a1&!a0) | (!a7&!a6&!a5&a4&!a3&!a2&!a1&!a0); y1 = (a7&!a6&!a5&!a4&!a3&!a2&!a1&!a0) | (!a7&a6&!a5&!a4&!a3&!a2&!a1&!a0) | (!a7&!a6&!a5&!a4&a3&!a2&!a1&!a0) | (!a7&!a6&!a5&!a4&!a3&a2&!a1&!a0); y0 = (a7&!a6&!a5&!a4&!a3&!a2&!a1&!a0) | (!a7&!a6&a5&!a4&!a3&!a2&!a1&!a0) | (!a7&!a6&!a5&!a4&a3&!a2&!a1&!a0) | (!a7&!a6&!a5&!a4&!a3&!a2&a1&!a0); z = (a7&!a6&!a5&!a4&!a3&!a2&!a1&!a0) | (!a7&a6&!a5&!a4&!a3&!a2&!a1&!a0) | (!a7&!a6&a5&!a4&!a3&!a2&!a1&!a0) | (!a7&!a6&!a5&a4&!a3&!a2&!a1&!a0) | (!a7&!a6&!a5&!a4&a3&!a2&!a1&!a0) | (!a7&!a6&!a5&!a4&!a3&a2&!a1&!a0) | (!a7&!a6&!a5&!a4&!a3&!a2&a1&!a0) | (!a7&!a6&!a5&!a4&!a3&!a2&!a1&a0);

2B

| s₂ | s₁ | s₀ | Output (y) |

|---|---|---|---|

| 0 | 0 | 0 | d₀ |

| 0 | 0 | 1 | d₁ |

| 0 | 1 | 0 | d₂ |

| 0 | 1 | 1 | d₃ |

| 1 | 0 | 0 | d₄ |

| 1 | 0 | 1 | d₅ |

| 1 | 1 | 0 | d₆ |

| 1 | 1 | 1 | d₇ |

| y = s₂’s₁’s₀’d₀ + s₂’s₁’s₀d₁ + s₂’s₁s₀’d₂ + s₂’s₁s₀d₃ + s₂s₁’s₀’d₄ + s₂s₁’s₀d₅ + s₂s₁s₀’d₆ + s₂s₁s₀d₇ |

2C

| y2 | y1 | y0 | a’ | b’ | c’ | d’ | e’ | f’ | g’ |

|---|---|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

| 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 |

| 1 | 0 | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 1 |

| 1 | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 |

| 1 | 1 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 |

| 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 |

✏️ Execises

2.2 A

B

C

switch2display

`timescale 1 ns / 1 ps

module switch2display_tb ();

// Signal declarations

logic [7:0] sw;

logic a7, a6, a5, a4, a3, a2, a1, a0;

logic a,b,c,d,e,f,g;

// Generate test vector.

initial begin

#0 sw = 8'b00000000;

#100 sw = 8'b00000001;

#100 sw = 8'b00000010;

#100 sw = 8'b00000100;

#100 sw = 8'b00001000;

#100 sw = 8'b00010000;

#100 sw = 8'b00100000;

#100 sw = 8'b01000000;

#100 sw = 8'b10000000;

end

// Unpack test vector to separate signals.

assign {a7, a6, a5, a4, a3, a2, a1, a0} =sw;

// Connect test signals to encoder8 module ports.

switch2display dut(.sw7(a7), .sw6(a6), .sw5(a5), .sw4(a4), .sw3(a3), .sw2(a2), .sw1(a1), .sw0(a0),

.a(a),.b(b),.c(c),.d(d),.e(e),.f(f),.g(g)

);

endmoduletestbench

`timescale 1 ns / 1 ps

module switch2display_tb ();

// Signal declarations

logic [7:0] sw;

logic a7, a6, a5, a4, a3, a2, a1, a0;

logic a,b,c,d,e,f,g;

// Generate test vector.

initial begin

#0 sw = 8'b00000000;

#100 sw = 8'b00000001;

#100 sw = 8'b00000010;

#100 sw = 8'b00000100;

#100 sw = 8'b00001000;

#100 sw = 8'b00010000;

#100 sw = 8'b00100000;

#100 sw = 8'b01000000;

#100 sw = 8'b10000000;

end

// Unpack test vector to separate signals.

assign {a7, a6, a5, a4, a3, a2, a1, a0} =sw;

// Connect test signals to encoder8 module ports.

switch2display dut(.sw7(a7), .sw6(a6), .sw5(a5), .sw4(a4), .sw3(a3), .sw2(a2), .sw1(a1), .sw0(a0),

.a(a),.b(b),.c(c),.d(d),.e(e),.f(f),.g(g)

);

endmodulemux8

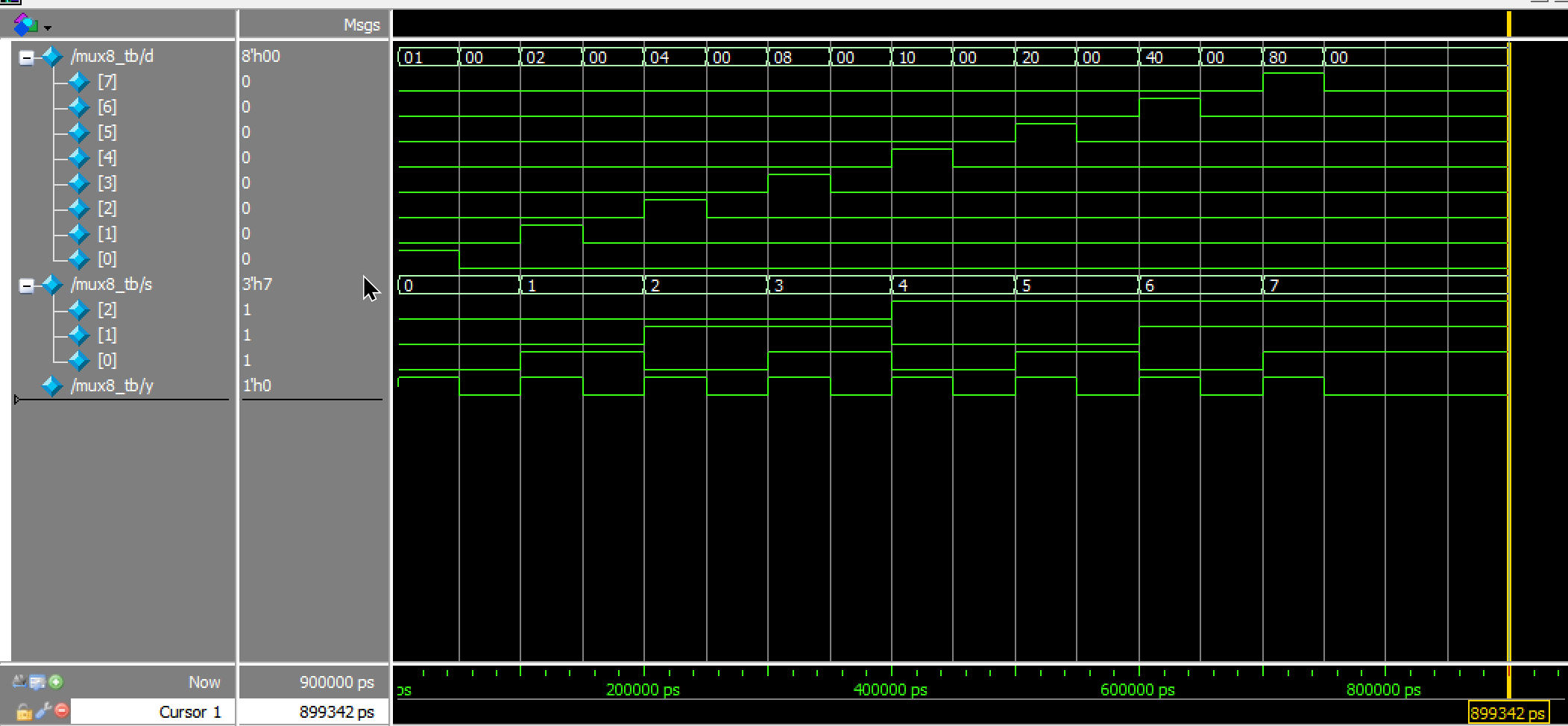

module mux8 (input logic d7, d6, d5, d4, d3, d2, d1, d0,

input logic s2, s1, s0,

output logic y);

// Complete module description here.

assign y = !s2&!s1&!s0&d0 | !s2&!s1&s0&d1 | !s2&s1&!s0&d2 | !s2&s1&s0&d3 | s2&!s1&!s0&d4 | s2&!s1&s0&d5 | s2&s1&!s0&d6 | s2&s1&s0&d7;

endmoduleencoder

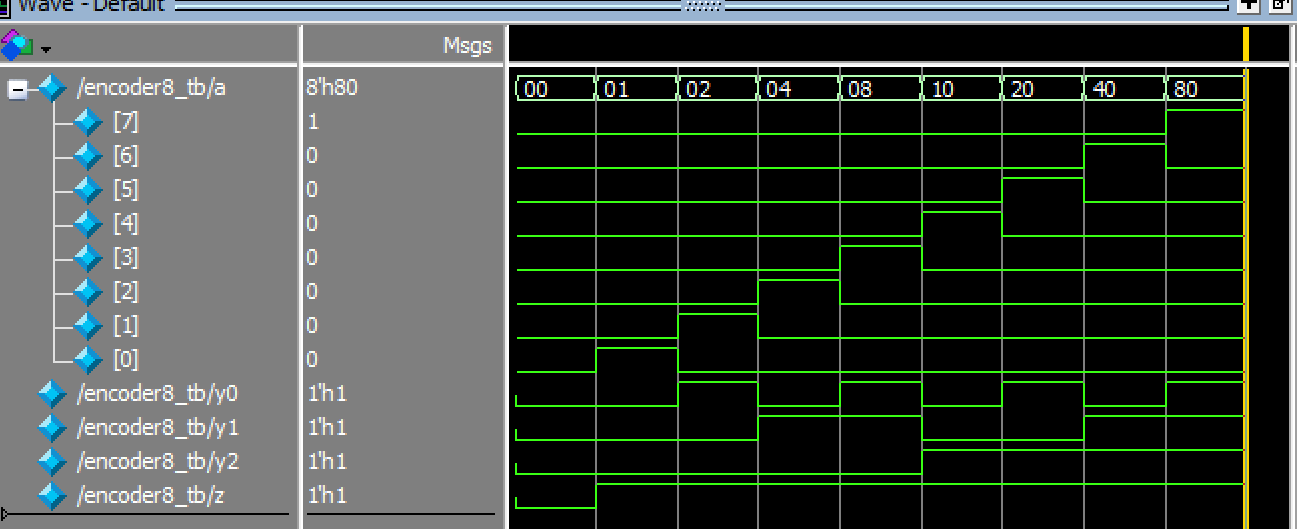

module encoder8 (input logic a7, a6, a5, a4, a3, a2, a1, a0,

output logic y2, y1, y0,

output logic z);

// Complete module description here.

assign y2 = (a7&!a6&!a5&!a4&!a3&!a2&!a1&!a0) | (!a7&a6&!a5&!a4&!a3&!a2&!a1&!a0) | (!a7&!a6&a5&!a4&!a3&!a2&!a1&!a0) | (!a7&!a6&!a5&a4&!a3&!a2&!a1&!a0);

assign y1 = (a7&!a6&!a5&!a4&!a3&!a2&!a1&!a0) | (!a7&a6&!a5&!a4&!a3&!a2&!a1&!a0) | (!a7&!a6&!a5&!a4&a3&!a2&!a1&!a0) | (!a7&!a6&!a5&!a4&!a3&a2&!a1&!a0);

assign y0 = (a7&!a6&!a5&!a4&!a3&!a2&!a1&!a0) | (!a7&!a6&a5&!a4&!a3&!a2&!a1&!a0) | (!a7&!a6&!a5&!a4&a3&!a2&!a1&!a0) | (!a7&!a6&!a5&!a4&!a3&!a2&a1&!a0);

assign z = (a7&!a6&!a5&!a4&!a3&!a2&!a1&!a0) | (!a7&a6&!a5&!a4&!a3&!a2&!a1&!a0) | (!a7&!a6&a5&!a4&!a3&!a2&!a1&!a0) | (!a7&!a6&!a5&a4&!a3&!a2&!a1&!a0) | (!a7&!a6&!a5&!a4&a3&!a2&!a1&!a0) | (!a7&!a6&!a5&!a4&!a3&a2&!a1&!a0) | (!a7&!a6&!a5&!a4&!a3&!a2&a1&!a0) | (!a7&!a6&!a5&!a4&!a3&!a2&!a1&a0);

endmodulenand

module nand_gate (input logic a, b,

output logic y

);

assign y = !(a&b);

endmodule